逻辑设计和硬件控制语言HCL

4.2逻辑设计和硬件控制语言HCL

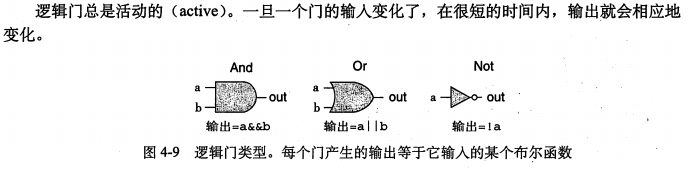

4.2.1 逻辑门

4.2.2 组合电路和HCL布尔表达式

将很多的逻辑门组合成一个网,就能够构建计算块,称为组合电路。构建这些网有两条限制:

- 两个或多个逻辑门的输出不能连在一起。否则它们可能会使线上的信号矛盾,可能会导致一个不合法的电压或电路故障。

- 这个网必须是无环的。也就是在网中不能有路经过一系列的门而形成一个回路,这样的回路会导致该网络计算的函数有歧义。

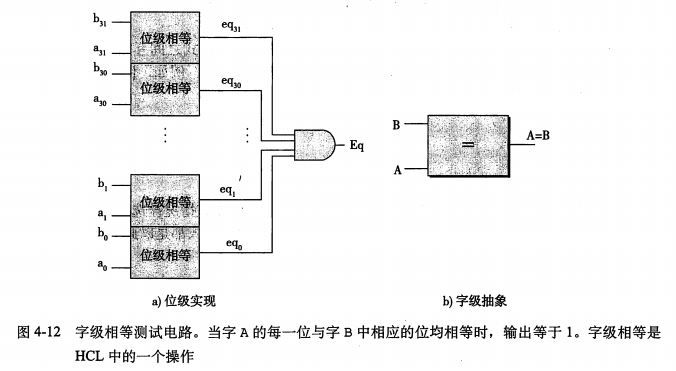

4.2.3 字级的组合电路和HCL整数表达式

通过将逻辑门组合成大的网,可以构造出能计算更加复杂函数的组合电路。通常,我们设计能对数据字(word)进行操作的电路。

执行字级计算的组合电路根据输入字的各个位,用逻辑门来计算输出字的各个位。例如图4-12中的一个组合电路,它测试两个32位字A和B是否相等。也就是,当且仅当A的每一位都和B的相应位相等时,输出才为1。

上图所示的电路的函数可以在字级别上表达成:

上图所示的电路的函数可以在字级别上表达成:

bool Eq = (A == B);

4.2.4 集合关系

4.2.5 存储器和时钟

组合电路从本质上讲,不存储任何信息。它们只是简单地响应输入信号,产生等于输入的某个函数的输出。为了产生时序电路,也就是有状态并且在这个状态上进行计算的系统,我们必须引入按位存储信息的设备。存储设备都是由同一个时钟周期控制,时钟是一个周期性信号,决定什么时候要把新值载入到设备中。

- 时钟寄存器(简称寄存器),存储单个位或字。时钟信号控制寄存器加载输入值。

- 随机访问存储器(简称存储器),存储多个字,用地址来选择该读或该写哪个字。